# Design of low power phased lock loop by using TSPC D-flipflop

# <sup>1</sup>Pullela Pavani, <sup>2</sup>Tanniru Aparna, <sup>3</sup>Uppala Bala Sri, <sup>4</sup>Ravipati Samyuktha, <sup>5</sup>G. Mounika, <sup>6</sup>Dr.Syed N Parveen

<sup>1</sup>BTech Student, Dept.of ECE, Malineni Lakshmaiah Womens Engineering College, Guntur, AP <sup>2</sup>BTech Student, Dept.of ECE, Malineni Lakshmaiah Womens Engineering College, Guntur, AP <sup>3</sup>BTech Student, Dept.of ECE, Malineni Lakshmaiah Womens Engineering College, Guntur, AP

<sup>4</sup>BTech Student, Dept.of ECE, Malineni Lakshmaiah Womens Engineering College, Guntur, AP

<sup>5</sup>Assistant Professor (M.Tech), Dept.of ECE, Malineni Lakshmaiah Womens Engineering College, Guntur, AP

<sup>6</sup>Associate Professor(Ph.D), Dept.of ECE ,Malineni Lakshmaiah Womens Engineering College, Guntur, AP

**Abstract**: Phase Locked loop (PLL) is a vital component in many applications. Here the design of the PLL to operate the frequency multiplier is considered. Frequency doubler operation is implemented with the help of the use of pre-prepared good judgment circuits in a Single-Phase Rectifier Clock Position (MTSPC) D flip-flop in a Phase Frequency Detector (PFD. Preset able Modified Single-Phase Clock (MTSPC) D flipflops functions run at a breakneck speed with lower power consumption. Noise is added in the form of system errors during D-flip (TSPC) use of the pre-selected single segment in the locked loop. A preset amplitude switched TSPC (MTSPC) D flip-flop is used to overcome glitches caused by triggering the output with PMOS. The technology used is 90 nm technology. In applications that require a higher rate and lower power consumption, this type of phase-locked loop (PLL) can be used.

Keywords: Preset able Modified Single-Phase Clock, Phase Locked loop, TSPC D-flipfloP.

## I. INTRODUCTION

With the development of technology, the overall performance of digital devices has been dramatically improved, and power consumption has become a critical issue for digital systems. Moreover, with the rapid improvement of the Internet of Things (IoT), IoT devices are being widely deployed [1]. In such battery-powered or self-powered devices, low-power design becomes the point of interest. As major components, the strength of flip-flops (FF) represents a massive component of the strength of digital structures. Therefore, reducing the power consumption of FFs can significantly reduce the power consumption of digital systems.

A potentiometer approach is an attractive approach to reducing the power consumption of digital systems. It is

#### C INTERNATIONAL

necessary to design an FF filter capable of operating at both the first-level threshold and near/sub-supply voltage to take advantage of the power advantages of the potentiometer method.

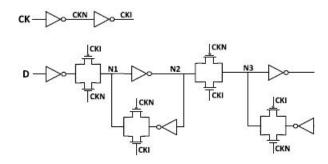

Gate flip flop (TGFF) is the most widely used in modern digital systems. Figure 1 shows the TGFF diagram. TGFF represents a competition-free FF scheme suitable for near-threshold operations. The disadvantage of TGFF main is its extensive clock network. The internal nodes CKN and CKI switch independently of the input registers, and the CKN and CKI nodes feed a more significant number of transistors. Thus, the electricity input to the TGFF is still significant even though the interest in registration is still low. The uses of complementary clock flags should be optimized to reduce the power consumption of FF

Fig.1 Schematic of TGFF.

Several low-energy unpaired FFs have been suggested in previous work. Nevertheless, some problems impact the electricity consumption of those FF. For

Issue II

filters fail example, some at low conduction voltages and some suffer from high amperage before the rate. This publication proposes а low-energy mismatched FF (TSPC) to solve these problems. The proposed FF is not subject conflict and is suitable for to comprehensive supply voltage operation. addition, pre-tariff overrunning is In wholly dispensed with under the proposed FF, and, in addition, electricity taking is improved compared to previous low electric installations.

# II. REVIEW OF LITERATURE

Moumita Das et al. [2018] This document presents the current deprived VCO design using a pseudo-NMOS topology. The proposed design has better segment noise and lower power consumption compared to conventional CSVCOs, and the variety of components is much smaller (8 MOSFETs are reduced). The proposed design consists of five phases of the inverter, and a pseudo-NMOS topology is used to replace the current source PMOS blocks, reducing the power consumption to 155.7 LW for a base frequency of 1.8 GHz. Simulation effects show that the proposed CSVCO has better section noise and lower electricity consumption than different toroidal VCO topologies. The circuit performance was verified in a Cadence Specter using a 180 nm ERA CMOS with

# ISSN: 2366-1313

2022

C INTERNATIONAL

a 1.8 V source. The evaluation also indicates that for this CSVCO, the clip noise is (-103.73 dB/Hz) at an offset frequency of 1 MHz and (-124.97 dB/Hz) at an offset frequency of 10 MHz.

Noushin Ghaderi et al. [2016]A low power, low tension, non-divisible phase locking loop (PLL) is provided in this document. A more accessible open loop phase frequency detector (PFD) is which proposed, reduces power consumption and increases overall speed. A new size-driven Wilson price pump circuit has also been introduced, whose overall performance is more robust by using some optimization algorithms for high performance and ultra-contemporary matching. The designed PLL is used in a 0.18 µm CMOS process with a 1.8V power supply. It has a wide frequency locking range from 500MHz to 5GHz. Moreover. the overall vibration is significantly reduced using a segment without life, much less a PFD and PLL without a barrier.

Kaipu et al. [2016] This paper presents a low-power third-order fully locked loop (PLL) design with a wide bandwidth from 1.7 GHz to 2.5 GHz using UMC180nm CMOS technology. The designed model

features conventional frequency а synthesizer architecture entirely based on Integer-N PLL with design the modifications in the voltage control oscillator (VCO). The results from the published format show that the vibration of the PLL after it is stabilized at a frequency of 2 GHz at 14.1 µs is about 35.26 ps. The total power consumption of the PLL is 274.346 uW while operating at 1.4/1.8 V at an output frequency of 2 GHz. This design occupies an area of 11,862 mm2 and can be used for ZigBee applications.

Nanda et al. [2013] This document explores a phase closed loop (PLL) design that can accommodate various frequencies used for GSM software. PLL is used for wireless conversation within the GHz band to correct section and frequency errors and synchronization provides with low blocking time and minimized drift and jitter. PLL is used in many processing elements to provide clock synchronization and reset. The above basic programs require a phase-locked loop design with low clip noise, low time lock, and high capture diversity. The PLL design operates on 90nm mode technology (GPDK 090) in analog clock design environment an achieving a frequency range of 250MHz to 950MHz. This PLL has a clipping noise of 91.74 dB/Hz at a frequency shift of 1 MHz,

351

# ISSN: 2366-1313

## ISSN: 2366-1313

where the blocking time is 220 ns, which is much less.

Ravisaheb et al. [2017]Phase detectors determine the relative section difference between the two incoming indicators and output a signal proportional to that phase difference. Phase detector also detects frequency error; They are known as Phase Frequency Detectors (PFDs). It can be a fundamental data recovery block and clock circuit. This document presents unique design schemes for color balance mapping and compares them to its output results. PFD is implemented according to to single-phase timing standards. The circuits considered are PFD using NAND gate, PFD using NOR gate, and PFD using AND gate. Unique PFD circuits designed and simulated in LT Spice Tool using 45nm CMOS method technology with 1V supply voltage.

Sandhiya et al.[2018]The voltagecontrolled oscillator is at the heart of many modern electronic and verbal exchange devices. Therefore, the VCO may be required to operate in the GHz frequency band. This assignment describes a design and implementation of a current-hungry five-voltage CMOS oscillator for a phaseclosed loop. The current-hungry VCO is a simple toroidal oscillator coupled to series transformers. The proposed circuit is implemented in zero-generation CMOS, 18 µm. By changing the VCO control voltage from 0.5 to 4.5 V, the tuning range from 81.85 MHz to 2.433 GHz is achieved. The phase noise at the offset frequency of 2.4GHz is -89.0307dBc/Hz. This project specializes in the design of low-power consumption and high-frequency VCO diversity. The current voltage-hungry controlled oscillator was designed using 180 nm GPDK CMOS technology with a supply voltage of 1.8 V and using the CADENCE spectrum tool. Cadence's Virtuoso Analog Design Environment was used to design and simulate the schematic for subsequent design.

#### III. PHASE LOCKED LOOP

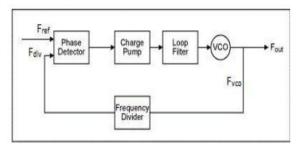

#### Fig. Phase locked loop

The PFD is observed using the charge pump, and the loop is clear, accompanied by the VCO and the bureaucracy of the frequency divider PLL, as shown. PFD compares the frequency of the signal and the reference signal divided by the frequency of the VCO. The output that drives the charge pump is a pulse. This pulse is a tonal variation of the input alerts. The output of the charge pump is used to

## ISSN: 2366-1313

increase or decrease the handling effort of the VCO or to maintain it as such.

# IV. PHASE FREQUENCY DETECTOR

#### **PFD using static D Flipflop**

PFD sheets constitute a significant block Divergence detection of PLL. alerts partition entry and is vital to many packages. The traditional PFD constructed using а D flip-flop has several disadvantages, such as high-power consumption, useless space, and transverse operating speed. It also takes up more space since the number of transistors is extra. Reflectors have been added here as delay circuits to reduce the dead zone.

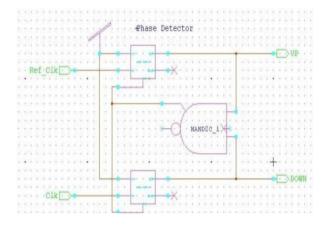

Fig PFD

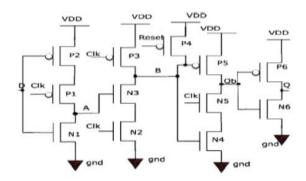

## PFD using preset able TSPC D flipflop

The TSPC Preset D flip flops are designed with a much smaller number of transistors and therefore take up a smaller footprint. An easy change that reduces internal switching was completed on some nodes of those bumps to reduce power consumption. Only one hour is performed for synchronization. This makes the circuit easier.

Fig positive edge triggered TSPC D Flipflop

Preset able TSPC D flipflop circuitis mainly designed using NMOS commongate inputs and PMOS transistors. Propagation delay is reduced with this type of transistor; thus, phase errors caused by waste areas are managed. The input remains separate from the output as long as the low signal is available over the clock. Therefore, the previous cost is kept at Qb when the clock signal is low or high. Once the clock signal goes from low to high, the output will produce the input's complement. The output keeps its high value until the reset is low.

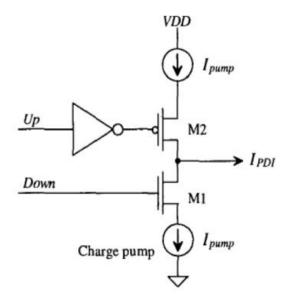

#### V. CHARGE PUMP

The charge pump controls the VCO voltage according to the up or down signals obtained from the PFD. The charge related to the NMOS and PMOS valve

builds a charge pump. The entrance is the up or down signal from the PFD. The PFD produces an upward signal when the reference signal is excessive compared to the VCO feedback signal. This, in turn, will activate the PMOS in the velocity pump and velocity pump and then pump the talk into the loop filter. The output voltage is high. The PFD produces a low signal when the reference signal is low compared to the VCO feedback signal. When this low signal is given as input to the price pump, it will shift the NMOS to the position and cause the current loop filter to pull back. The output voltage can be reduced. Equal currents flow in NMOS and **PMOS** avoid leading-edge to mismatch.

Fig. Charge Pump

# **VI. SIMULATION RESULTS**

Issue II

ISSN: 2366-1313

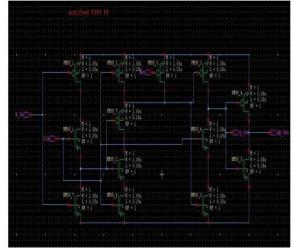

## Fig. MTSPC D Flipflop

To eliminate switching conditions, the MTSC D flip-flop was designed by adding an additional PMOS transistor using a gifted 90 nm timing generation as described above. The switch mode operation of the MTSPC D flip-flop is shown. The 4GHz clock frequency is implemented at a simulation time of 10ns.

354

# Fig Output diagram of MTSPC D Flipflop

# Table I. Comparison of TSPC DFF and MTSPC DFFparameters

| Performance<br>parameters          | TSPC DFF  | MTSPC DFF |

|------------------------------------|-----------|-----------|

| Input clock frequency              | 1 GHz     | 1 GHz     |

| Clock-to-Q delay (Low-<br>to-High) | 92.95 ps  | 61.08 ps  |

| Clock-to-Q delay (High-<br>to Low) | 143.6 ps  | 122.9 ps  |

| Average Clock-to-Q<br>delay        | 118.27 ps | 91.99 ps  |

| Setup time(tsetup)                 | 70.13 ps  | 64.14 ps  |

| Hold time(theld)                   | ≈ 0       | ≈ 0       |

| Average power<br>consumption       | 75.43 μW  | 21.83 µW  |

The performance of each TSPC D flip-flop and MTSPC D flip-flop is compared with an identical clock frequency of 1 GHz. MTSC D flip-flop proposes favorable overall performance compared to the TSPC D flip-flop in terms of lower delay and power consumption.

# **VII. CONCLUSION**

An efficient design of MTSPC D flip-flop PFD for PLL is provided. Synchronous dynamic logic is used. A single clock frequency of 1 GHz was used. In a conventional PLL circuit, D flip-flops are used in the PFD block. This leads to glitches, which are the main cause of part errors. Therefore, to avoid these

drawbacks. pre-prepared **MTSPC** а inverter has been provided in this document. Compared with standard TSPC flip-flops, these flip-flops have reduced noise at the output. The energy was eaten up with the help of the built circuit and became much less. By adding PMOS, changes in intermediate nodes are avoided. Since the MTSPC flip-flop has benefits such as high-speed operation, low noise, and low electricity consumption, it can be applied in many electronic circuits where all these parameters are vital. PLL is designed using MTSPC flip-flop, which can be used in clock technology, frequency synthesizer, and clock recovery circuit in serial recording hyperlinks. So it is not only useful for other PLL circuits where D flip-flops are applied, it can be replaced with MTSPC flip-flops for better performance.

# REFERENCES

[1] L. Atzori, A. Iera, and G. Morabito,

"The Internet of Things: A survey,"*Comput. Netw.*, vol. 54, no. 15, pp. 2787–2805, Oct. 2010.

[2] T. Tekeste, H. Saleh, B. Mohammad, A. Khandoker, and M. Ismail,"A nano-watt ECG feature extraction engine in 65-nm technology,"*IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 8, pp. 1099–1103,Aug. 2018.

[3] T. Tekeste, H. Saleh, B. Mohammad, and M. Ismail, "Ultra-low powerQRS detection ECG compression and architecture for IoT healthcaredevices," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 66, no. 2, pp. 669-679, Feb. 2019.

[4] A. Pullini, D. Rossi, I. Loi, G. Tagliavini, and L. Benini, "Mr. Wolf:An energy-precision scalable parallel ultra low power SoC for IoT edgeprocessing," IEEE J. Solid-State Circuits, vol. 54, no. 7, pp. 1970–1981, Jul. 2019.

[5] J. P. Cerqueira, T. J. Repetti, Y. Pu, S. Priyadarshi, M. A. Kim, and M. Seok, "Catena: A near-threshold, sub-0.4-mW, programmablespatial 16-core array accelerator for the ultralow-power mobile andembedded Internet of Things," IEEE J. Solid-State Circuits, vol. 55,no. 8, pp. 2270-2284, Aug. 2020.

[6] Das, M., P. Mostafa, A. Pal, D. Das, and S. Chatterjee. 2018. "Design of an energy efficient, low phase noise currentstarved VCO using pseudo-NMOS logic". In Advances in Communication, Devices and Networking, 35-42. Lecture Notes in Electrical Engineering, vol. 462. Springer https://doi.org/10.1007/978-Singapore. 981-10-7901-6 5

[7] Ghaderi, N., H. R. Erfani-jazi, and M. Mohseni-Mirabadi. 2016. "A low noise, power phaselocked loop, low using

optimization methods". Journal of Electrical and Computer Engineering 2016: Article ID 8202581. https://doi.org/10.1155/2016/8202581.

[8] Kaipu, S. V. R., K. Vaish, S. Komatireddy, A. Sood, and M. Goswami. 2016. "Design of a low power wide range phase locked loop using 180nm CMOS technology". International In 2016 Conference on Signal Processing and Communication (ICSC), 443-47. IEEE. https://doi.org/10.1109/ICSPCom.2016.79 80621.

[9] Nanda, U., D. P. Acharya, and S. K. Patra. 2013. "Design of a low noise PLL for GSM application". In Proceedings -2013 International Conference on Circuits, Controls and Communications, CCUBE 2013, Article number 6718578. IEEE. https://doi.org/10.1109/CCUBE.2013.6718 578.

[10] Ravisaheb, H. B., and B. H. Nagpara. 2017. "Design and implementation of phase frequency detector using different logic gates in 45nm CMOS process technology". International Research Journal of Engineering and Technology 4, no. 2 (february): 189-93.

[11] Salunke D, Peddi Prasadu, Mane D, Joshi R. Customized convolutional neural network to detect dental caries from radiovisiography (RVG) images

#### ISSN: 2366-1313

InternationalJournalofAdvancedTechnology and EngineeringExploration.2022;9(91):827-838.DOI:10.19101/IJATEE.2021.874862.